| Vektonechner                                  |

|-----------------------------------------------|

| 1.1. 7 2.8. 64-bét CPU nutzen, cun            |

| 8 Operationen gleichzeitig ausz               |

| fulsen.                                       |

| 1.21 Pipelining (instruction pipelin          |

| 1 Maschineentefell (Z.B.<br>12 ADD \$64 [REG] |

| 12 ADD \$64 [REG]                             |

| sind in real melitere CPU-Takte, 2.7          |

| Fetzh: lese Befehl                            |

| Decode: de Kodille                            |

| Execute hole Defen œus speicher und filme œus |

| Write: 6 derei de Ergebnis                    |

| Trick: diese schrikk verschachteln            |

|                                               |

|                                               |

| <br>   |    |    | F4 |    |    |

|--------|----|----|----|----|----|

| <br>   |    |    | -  |    |    |

| <br>   |    |    | D3 |    | W3 |

| <br>   | F2 | D2 | EZ | W2 |    |

| <br>F1 | D1 | CA | W1 |    |    |

| <br>   |    |    |    |    |    |

Probleme bendbiet bei [1.1]: • Datentiansport wird zeem Engpass Dafen mussen hintereinander im speicher stehen (oeber so teen alsob) # Hin- & Herschalten zwischen Stever-& Daten-Operationen (IF vs. ADD) bei [1,2] . Woerten bei a:= a:-1+5 worten, bis a i-1 geschrieben ist Crays losen das, indem somelle Steverbefehle realistert werden; und optimiert speichtzugriff durch viele Registerspeicher; CPV RAM ( ( a 10 B) (billing) Reg. 8 (Rechly-48ng 6ng & sey encly) Zugnffszect (teuer)

Aufden 20ben Daku: 2.B a; = 20; 1+5-0:-2

| Also Doky longe in Register hollen<br>Treal stockt in Crays noch viel weber; aber ok] |

|---------------------------------------------------------------------------------------|

| Freal steckt in Crays north viel well, aber ok ]                                      |

| [ Melwere Prozessoren bzw. Karne                                                      |

| Oben lait ja zunechst immer noch<br>nur ein Programm ab- Verzoche das                 |

| vir oblin zu beschleumpen:  • Experimente Zugen, doss jenseits                        |

| von 4 Prozessoren Kaum Verbesserun-                                                   |

| ger ent seven                                                                         |

| · Erfordort Komplexes Scheduling                                                      |

| Also: Melykemprozessoren                                                              |

| (melutre vollwertige CPUs auf                                                         |

| einem chip)                                                                           |

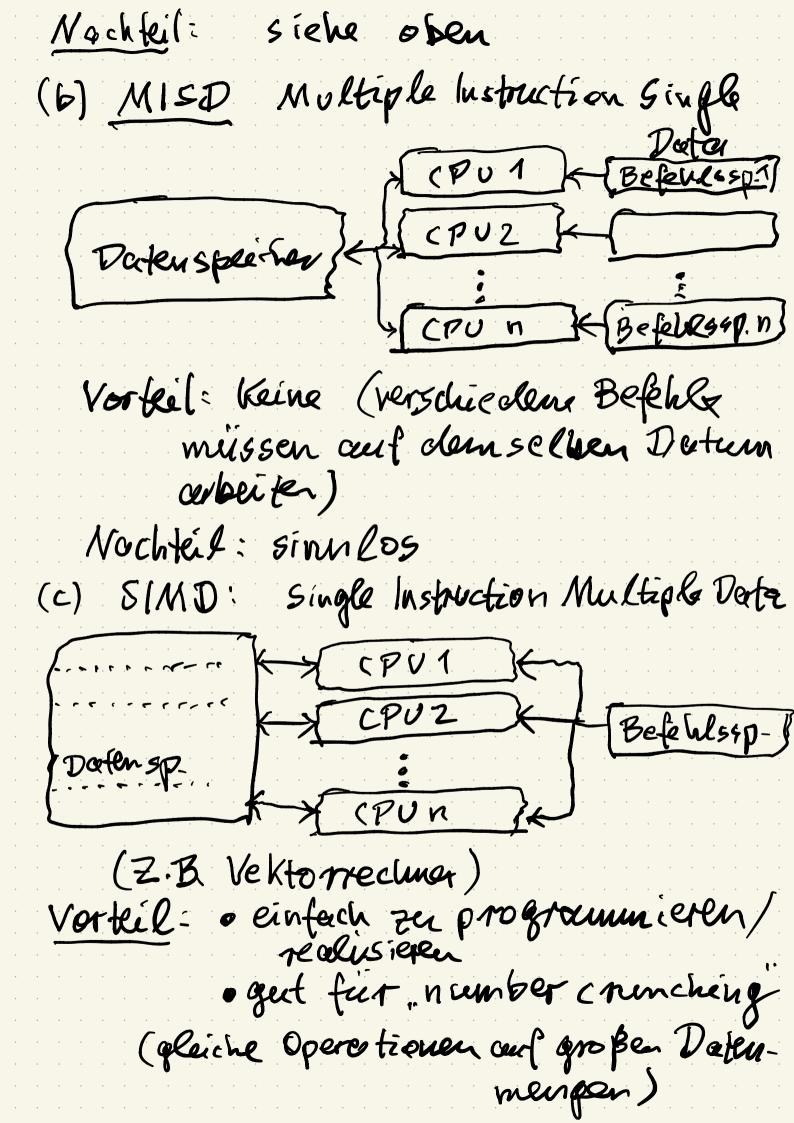

| Flynnsche Klassifiziereng<br>Ein Votschlag der Klassifizierung<br>(SISD, SIND.)       |

| Ein Vorschlag der Klassifizierung                                                     |

| (SISD, SIMD.).)                                                                       |

| (a) SISD Single Instruction Single Dota                                               |

| Datenspeida (PU) Refebbs-<br>speida                                                   |

|                                                                                       |

| (von-Neumann-Architekter)<br>Vorteil: « einfoch zu benutzen & reclisique              |

|                                                                                       |

## Klufe Organisation.

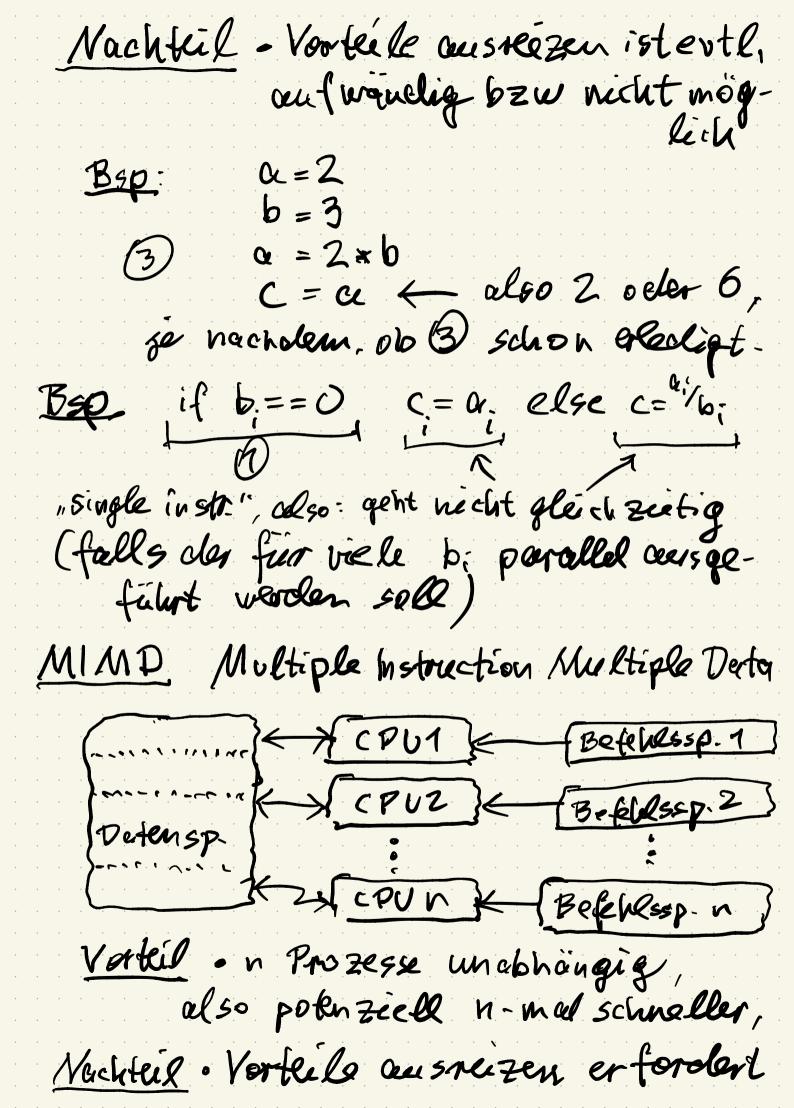

Proktisch alle Gerate (PC, Laptop, Hundy) heat sind MIND-: Cluster mit Auch "Supercomposer" met 1000en GPUS

## 2. Netzwerktopologee

Beispiele oben zeigen bereitz, clæss der Speicherzugriff Klug organistert verdon huss.

Teil dessen: Wie genou CPUs mit don speicher vernetzt sind.

· Ideal peler mit jeden: physisch nicht machber.

Also anders regelu:

- Topologie (Gestalt)

- Routing (wer wo læng)

Switching (stückeln, Ampeln",

Weichen")

Zur Topologie: Lnich ste Vorlesung)